- 您现在的位置:买卖IC网 > Sheet目录3753 > ATMEGA169P-16MCHR (Atmel)MCU AVR 16KB FLASH 16MHZ 64-VQFN

83

8018P–AVR–08/10

ATmega169P

Note:

1. AIN0D and AIN1D is described in ”DIDR1 – Digital Input Disable Register 1” on page 215.

13.3.6

Alternate Functions of Port F

The Port F has an alternate function as analog input for the ADC as shown in Table 13-18. If

some Port F pins are configured as outputs, it is essential that these do not switch when a con-

version is in progress. This might corrupt the result of the conversion. If the JTAG interface is

enabled, the pull-up resistors on pins PF7(TDI), PF5(TMS) and PF4(TCK) will be activated even

if a reset occurs.

TDI, ADC7 – Port F, Bit 7

ADC7, Analog to Digital Converter, Channel 7.

TDI, JTAG Test Data In: Serial input data to be shifted in to the Instruction Register or Data Reg-

ister (scan chains). When the JTAG interface is enabled, this pin can not be used as an I/O pin.

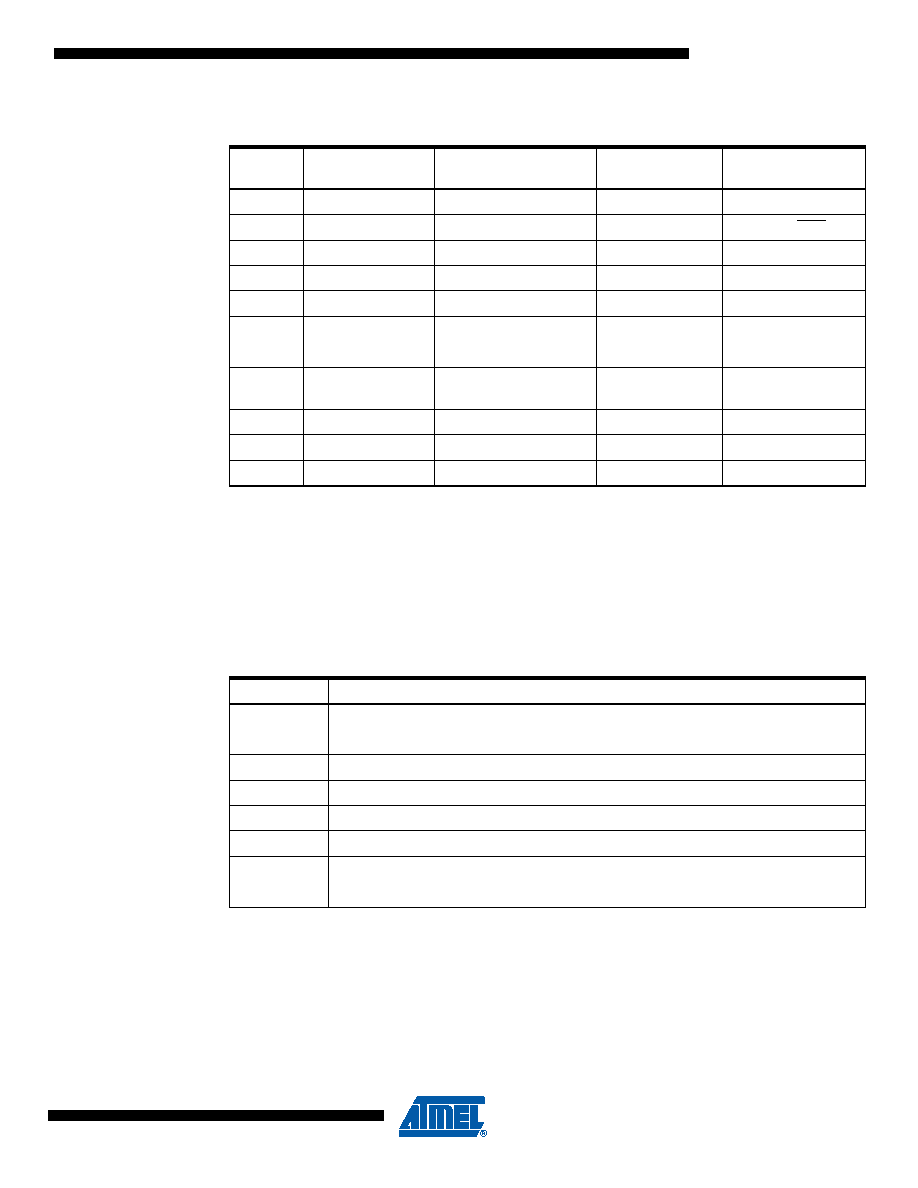

Table 13-17. Overriding Signals for Alternate Functions in PE3:PE0

Signal

Name

PE3/AIN1/

PCINT3

PE2/XCK/AIN0/

PCINT2

PE1/TXD/

PCINT1

PE0/RXD/PCINT0

PUOE

0

TXENn

RXENn

PUOV

0

PORTE0 PUD

DDOE

0

TXENn

RXENn

DDOV

0

1

0

PVOE

0

XCK OUTPUT ENABLE

TXENn

0

PVOV

0

XCK

TXD

0

PTOE

–

DIEOE

(PCINT3 PCIE0)

+ AIN1D(1)

(PCINT2 PCIE0) +

AIN0D(1)

PCINT1 PCIE0

PCINT0 PCIE0

DIEOV

PCINT3 PCIE0

PCINT2 PCIE0

1

DI

PCINT3 INPUT

XCK/PCINT2 INPUT

PCINT1 INPUT

RXD/PCINT0 INPUT

AIO

AIN1 INPUT

AIN0 INPUT

–

Table 13-18. Port F Pins Alternate Functions

Port Pin

Alternate Function

PF7

ADC7/TDI (ADC input channel 7 or JTAG Test Data Input)

PF6

ADC6/TDO (ADC input channel 6 or JTAG Test Data Output)

PF5

ADC5/TMS (ADC input channel 5 or JTAG Test mode Select)

PF4

ADC4/TCK (ADC input channel 4 or JTAG Test ClocK)

PF3

ADC3 (ADC input channel 3)

PF2

ADC2 (ADC input channel 2)

PF1

ADC1 (ADC input channel 1)

PF0

ADC0 (ADC input channel 0)

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

2-1546217-0

TERM BLK RCPT 20POS SIDE 5.08MM

1-1546217-9

TERM BLK RCPT 19POS SIDE 5.08MM

1-1546217-8

TERM BLK RCPT 18POS SIDE 5.08MM

1-1546217-7

TERM BLK RCPT 17POS SIDE 5.08MM

1-1546217-6

TERM BLK RCPT 16POS SIDE 5.08MM

1-1546217-5

TERM BLK RCPT 15POS SIDE 5.08MM

1-1546217-4

TERM BLK RCPT 14POS SIDE 5.08MM

1-1546217-3

TERM BLK RCPT 13POS SIDE 5.08MM

相关代理商/技术参数

ATMEGA169P-16MCU

功能描述:8位微控制器 -MCU AVR 16KB, 512B EE 16MHz 1KB SRAM, 5V

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA169P-16MU

功能描述:8位微控制器 -MCU AVR 16K FLASH 512B EE 1K SRAM LCD ADC RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA169P-16MU SL383

制造商:Atmel Corporation 功能描述:MCU 8BIT ATMEGA RISC 16KB FLASH 3.3V/5V 64PIN MLF - Tape and Reel

ATMEGA169P-16MUR

功能描述:8位微控制器 -MCU AVR LCD 16KB FLSH EE 512B 1KB SRAM-16MHZ RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA169P-8AU

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:Microcontroller with 16K Bytes In-System Programmable Flash

ATMEGA169P-8MU

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:Microcontroller with 16K Bytes In-System Programmable Flash

ATMEGA169PA

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:8-bit Microcontroller with 16K Bytes In-System Programmable Flash

ATMEGA169PA_1

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:High Endurance Non-volatile Memory segments